DEGREE PROJECT IN SCHOOL OF ENGINEERING SCIENCE, DEPARTMENT OF APPLIED PHYSICS

SECOND CYCLE (30hp), SK202X

# Fabrication and characterization of $GaAs_xP_{1-x}$ single junction solar cell on GaAs/Si for III-V/Si tandem solar cell

**ELAHEH AGHAJAFARI**

# Fabrication and characterization of $GaAs_xP_{1-x}$ single junction solar cell on Si for III-V/Si tandem solar cell

Elaheh Aghajafari

January 2023

**Examiner:**

Prof. Anand Srinivasan

Supervisors:

Prof. Sebastian Lourdudoss- Dr. Yanting Sun-Axel Strömberg

#### **Abstract**

Silicon based solar cells have been used as photovoltaic devices for decades due to reasonable cost and environment- friendly nature of silicon. But the conversion efficiency of silicon solar cell is limited; for instance, the maximum conversion efficiency of a crystalline silicon solar cell available in the market developed by Kaneka Corporation is 26 % [1]. In comparison, III-V compound semiconductor multijunction solar cells are the most efficient solar cells with efficiency of 47.1% [2]. However, due to high-cost substrate materials, III-V solar cells are not the best option for large scale production in real life. Therefore, integration of III-V compound semiconductors on silicon substrate has been studied to obtain III-V/Si multi junction solar cells with high conversion efficiency with reasonable price. To this end, we studied epitaxial growth of  $GaAs_xP_{1-x}$  on GaAs deposited on Si.

This thesis presents the characterization results of the above  $GaAs_xP_{1-x}$  epitaxial layer and fabrication of a  $GaAs_xP_{1-x}$  single junction solar cell on GaAs coated Si substrate and its performance.

In the first part of the project,  $GaAs_xP_{1-x}$  epitaxial layer grown by Hydride Vapor Phase Epitaxy (HVPE) on different kinds of substrates at different growth conditions are characterized to identify the optimized growth conditions and a suitable substrate. Samples are characterized by High Resolution X-ray Diffraction (HRXRD) and photoluminescence (PL) to determine the composition of  $GaAs_xP_{1-x}$  and its crystalline quality and by optical microscope to assess the surface morphology. Scanning Electron Microscope (SEM) is used to study the depth of the dry etched structures.

The second part of the project deals with the fabrication process consisting of 21 steps to obtain a  $GaAs_xP_{1-x}$  single junction solar cell structure on GaAs/Si. This process flow will be explained in some detail along with a brief description of several tools in cleanroom that have been used for this purpose.

Finally, in the third part, devices are characterized to investigate their performance. Transmission Line Method (TLM) is used to obtain important parameters such as specific contact resistance. Current-voltage (I-V) relation of solar cell is investigated to acquire its efficiency. The lowest specific contact resistance measured in this project is  $7.4 \times 10^{-8} \ \Omega.\ cm^2$  for p-contact (for 4041DV- cell 8) and the highest efficiency measured is 1.64% (for 4041DV- cell 6).

In conclusion, although the results obtained are far from the state-of-the art results, this work has laid the foundation for future work that can lead to a breakthrough in fabricating multi-junction tandem solar cell on silicon.

Key words: III-V semiconductor,  $GaAs_xP_{1-x}$  heteroepitaxy, hydride vapor phase epitaxy, III-V/Si solar cell.

#### **Abstrakt**

Kiselbaserade solceller har använts i årtionden på grund av dess rimliga kostnad och miljövänliga natur. Omvandlingseffektiviteten för kiselsolcell är begränsad; till exempel är den maximala omvandlingseffektiviteten för solceller av kristallin kisel utvecklad av Kaneka Corporation 26 % [1]. Som jämförelse är III-V sammansatta halvledare multi-junction solceller de mest effektiva solcellerna med en effektivitet på 47,1 % [2]. På grund av de höga substratmaterialen är III-V-solceller i realiteter inte det bästa alternativet för storskalig produktion. Därför har integration av III-V sammansatta halvledare på kiselsubstrat studerats för att erhålla III-V/Si multi junction solceller med hög omvandlingseffektivitet till rimligt pris. För detta ändamål studerade vi epitaxiell tillväxt av  $GaAs_xP_{1-x}$  på GaAs avsatt på Si.

Denna avhandling presenterar karaktäriseringsresultaten av ovanstående  $GaAs_xP_{1-x}$  epitaxiella skikt och tillverkning av en  $GaAs_xP_{1-x}$  enkel förbindelse solcell på GaAs-belagt Si-substrat och dess prestanda.

I den första delen av projektet karaktäriseras  $GaAs_xP_{1-x}$  epitaxiallager odlat med Hydride Vapor Phase Epitaxy (HVPE) på olika typer av substrat vid olika tillväxtförhållanden för att identifiera de optimerade tillväxtförhållandena och ett lämpligt substrat. Prover kännetecknas av högupplöst röntgendiffraktion (HRXRD) och fotoluminescens (PL) för att bestämma sammansättningen av  $GaAs_xP_{1-x}$  och dess kristallina kvalitet och med optiskt mikroskop för att bedöma morfologin. Scanning Electron Microscope (SEM) används för att studera djupet av de torretsade strukturerna.

Den andra delen av projektet behandlar tillverkningsprocessen som består av 21 steg för att erhålla en  $GaAs_xP_{1-x}$  enda förbindelse solcellsstruktur på GaAs/Si. Detta processflöde kommer att förklaras i detalj tillsammans med en kort beskrivning av flera verktyg i renrum som har använts för detta ändamål.

Slutligen, i den tredje delen, karaktäriseras enheter för att frilägga dess prestanda. Transmission Line Method (TLM) används för att erhålla viktiga parametrar som specifikt kontaktmotstånd. Förhållandet mellan ström och spänning (I-V) hos solcellen undersöks för att uppnå optimal effektivitet. Den lägsta specifikt kontaktmotstånd som uppmätts i detta projekt är  $7.4 \times 10^{-8} \ \Omega.\ cm^2$  för p-kontakt (för 4041DV-cell 8) och den högsta uppmätta effektiviteten är 1.64% (för 4041DV-cell 6).

Sammanfattningsvis, även om de erhållna resultaten är långt ifrån de senaste resultaten inom forskning, lägger detta arbete grunden för framtida arbete som kan leda till ett genombrott i tillverkningen av multi-junction tandemsolcell på kisel.

Nyckelord: III-V halvledare –  $GaAs_xP_{1-x}$  epitaxiallager- hydridångfasepitaxi -III-V/Si solcell.

## Acknowledgments

First, I would like to thank Prof. Sebastian Lourdudoss for giving me a great opportunity to work in the semiconductor material group (HMA) in photonics department and Prof. Anand Srinivasan for having accepted to be my examiner. I would also like to thank Dr. Yanting Sun, my main supervisor, for his encouragement and help during the project.

I would like to say a special thanks to Dr. Axel Strömberg, my supervisor, for being always around to help me patiently in every possible way. I am so blessed to have an opportunity to work in such a great environment in the semiconductor group working with wonderful and knowledgeable researchers and to have a chance to meet new people from other groups and companies as well.

I also appreciate researchers, PhD students, and staffs in Electrum laboratory for tool training and other helps in the lab: they are Reza Nikpars, Olof Öberg, Mattias Ekström, Fei Ye and Cecilia Aronsson. I would also thank my dear friend Per-Ola Mård for helping me in Swedish translation. Finally, I would like to thank my beloved spouse, Euhanna and family who supported me during this project and having been very kind and patient.

Stockholm, January 2023 Elaheh Aghajafari

# **Table of contents**

| Al | ostra           | ct       |                                                   | iii |

|----|-----------------|----------|---------------------------------------------------|-----|

| Al | ostra           | kt       |                                                   | iv  |

| Ac | knov            | vledgm   | ents                                              | v   |

| Ta | ıble o          | of conte | nts                                               | vi  |

| Li | st of l         | Figures  |                                                   | vii |

|    |                 |          |                                                   |     |

| Li | st of a         | acronyi  | ms and abbreviations                              | xi  |

| 1  |                 | •        | on                                                |     |

|    | 1.1             |          | knowledge of solar cell                           |     |

|    | 1.2             | Objec    | tive of the thesis                                | 4   |

| 2  | Exp             | erimei   | ntal set up                                       | 7   |

|    | 2.1             | Low p    | ressure Hydride Vapor Phase Epitaxy (LP-HVPE)     | 7   |

|    | 2.2             | Chara    | cterization methods                               | 8   |

|    |                 | 2.2.1    | High Resolution X-Ray Diffraction (HRXRD)         |     |

|    |                 | 2.2.2    | Scanning Electron Microscopy (SEM)                |     |

|    |                 | 2.2.3    | Photoluminescence spectroscopy (PL)               |     |

|    |                 | 2.2.4    | Transmission Line Method (TLM)                    |     |

|    |                 | 2.2.5    | IV characterization                               | 12  |

|    | 2.3             | Fabric   | cation tools                                      | 15  |

|    |                 | 2.3.1    | Plasma Enhanced Chemical Vapor Deposition (PECVD) | 15  |

|    |                 | 2.3.2    | Photolithography                                  |     |

|    |                 | 2.3.3    | Inductively Coupled Plasma Etching (ICP)          | 17  |

|    |                 | 2.3.4    | Metal evaporation                                 | 17  |

| 3  | Crv             | stal qu  | ality optimization                                | 21  |

|    | 3.1             |          | th conditions                                     |     |

|    | 3.2             |          | acterization of the grown samples                 |     |

|    |                 | 3.2.1    | Crystal quality and composition                   |     |

|    |                 | 3.2.2    | Surface morphology                                |     |

| 4  | Cha             | racteri  | ization of sharp solar cell samples               | 38  |

| Т  | 4.1             |          | al quality and composition                        |     |

|    | 4.2             |          | ce morphology                                     |     |

| 5  |                 |          | fabrication                                       |     |

| 9  | 5.1             |          | ching process for III-V semiconductors            |     |

|    | 5.2             |          | tact formation                                    |     |

|    | 5.3             |          | ntact formation                                   |     |

| 6  | Sol             |          | characterization                                  |     |

| -  | 6.1             |          | neasurement                                       |     |

|    | 6.2             |          | nt-voltage (IV) characterization                  |     |

| 7  | Cor             |          | ns and future work                                |     |

| R  | R References 63 |          |                                                   |     |

# **List of Figures**

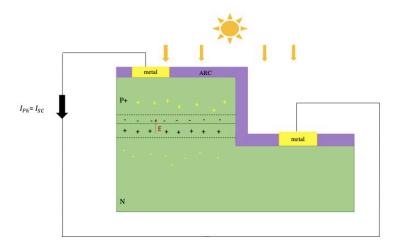

| Figure 1-1:  | Cross section of a solar cell at zero bias, where ARC means Anti                                          |    |

|--------------|-----------------------------------------------------------------------------------------------------------|----|

|              | Reflection Coating                                                                                        | 2  |

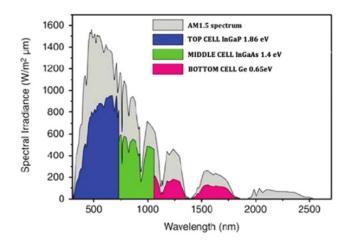

| Figure 1-2:  | Multiple layers of multi-junction solar cell absorbing specific range of Air mass 1.5 solar spectrum [6]. | 2  |

| Eiguno 1 2.  |                                                                                                           | C  |

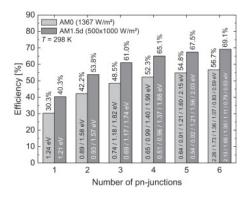

| Figure 1-3:  | Relation between number of pn-junctions in solar cell and the efficiency of it [9].                       | .3 |

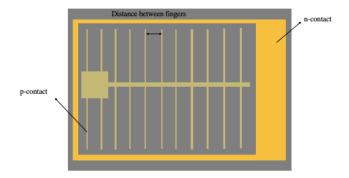

| Figure 1-4:  | Top view of a fabricated solar cell device in this project                                                |    |

| Figure 1-5:  | Detailed balance efficiency for dual junction series-connected solar cell                                 |    |

|              | under 1-sun AM1.5G. [10]                                                                                  | 5  |

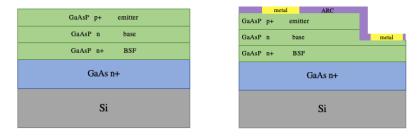

| Figure 1-6:  | Cross section of initial sample (left) and solar cell device (right)                                      | 5  |

| Figure 2-1:  | Schematic form of HVPE reactor [11]                                                                       | 7  |

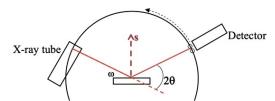

| Figure 2-2:  | Schematic form of Bragg's law [12]                                                                        | 8  |

| Figure 2-3:  | Schematic form of HRXRD tool [13]                                                                         | 8  |

| Figure 2-4:  | Configuration of HRXRD in double axis (a) and in triple axis (b) and                                      |    |

|              | their application in the thesis                                                                           | g  |

| Figure 2-5:  | (Left) Structure of scanning electron microscope (SEM) [14], (right)                                      |    |

|              | generation of various electrons in SEM [15]                                                               | 10 |

| Figure 2-6:  | (Left) Absorption and electron excitement, (right) light emission                                         | 10 |

| Figure 2-7:  | Schematic form of the TLM pattern of a solar cell.                                                        |    |

| Figure 2-8   | Plot of total resistance of the device vs contact distances                                               | 12 |

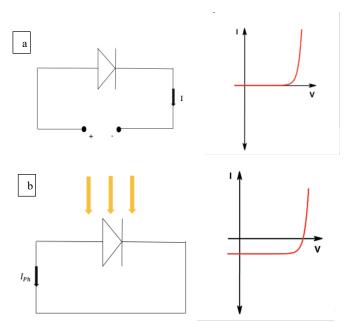

| Figure 2-9:  | Dark current curve of an ideal diode (a), diode with a series resistance                                  |    |

|              | (b) and diode with a shunt resistance (c) in linear scale                                                 |    |

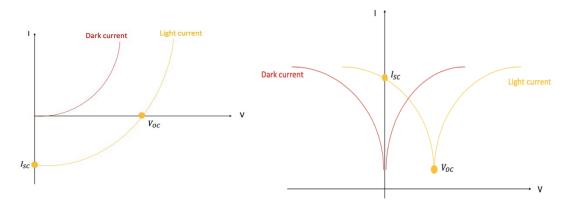

| Figure 2-10  | Light current curve of a solar cell in log scale                                                          | 14 |

| Figure 2-11: | PN junction of a solar cell in darkness (a) pn- junction of solar cell under                              |    |

|              | illumination (b) and corresponding IV curves in linear scale.                                             | 14 |

| Figure 2-12: | Dark and light current curve of a solar cell in linear scale (left) and in log                            |    |

|              | scale (right)                                                                                             |    |

| Figure 2-13: | Schematic form of PECVD [16].                                                                             |    |

| Figure 2-14: | Schematic form of Photolithography.                                                                       |    |

| Figure 2-15: | Schematic form of ICP [17]                                                                                | 17 |

| Figure 2-16: | Energy band diagram of metal and P-type semiconductor Schottky                                            | 40 |

| E' 0.45      | junction before (left) and after (right) equilibrium.                                                     | 18 |

| Figure 2-17: | Energy band diagram of metal and P-type Ohmic junction, tunnelling effect.                                | 19 |

| Figure 2-18: | Energy band diagram of metal and a N-type semiconductor Schottky                                          | 10 |

| rigure 2-10. | junction before (left) and after (right) equilibrium                                                      | 10 |

| Figure 2-19: | Energy band diagram of a N-type ohmic junction.                                                           |    |

| Figure 2-20: | Schematic form of metal evaporation tool [18]                                                             |    |

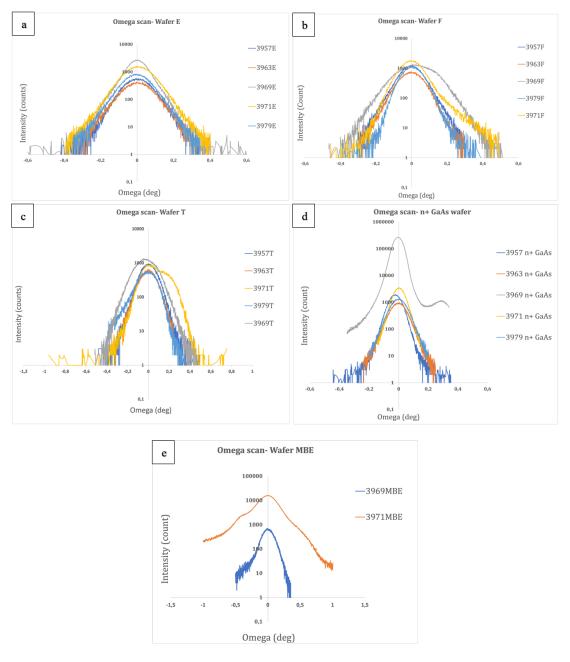

| Figure 3-1:  | Omega scan of samples in different runs.                                                                  |    |

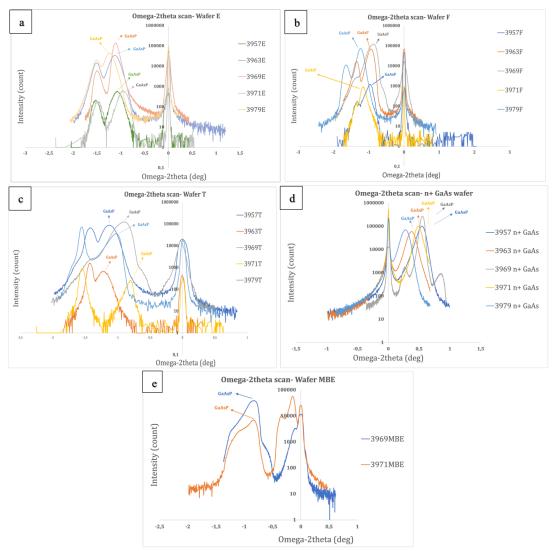

| Figure 3-2:  | Omega-2theta scan of samples in different runs.                                                           |    |

| Figure 3-3:  | Omega scan plots of a) wafer E, b) wafer F, c) Wafer T, d) n+ GaAs wafer                                  | 20 |

| rigare 5 5.  | and e) wafer MBE of different growth runs.                                                                | 28 |

| Figure 3-4:  | Omega-2theta plots of a) wafer E, b) wafer F, c) wafer T d) wafer n+                                      |    |

|              | GaAs and e) wafer MBE of different runs.                                                                  | 29 |

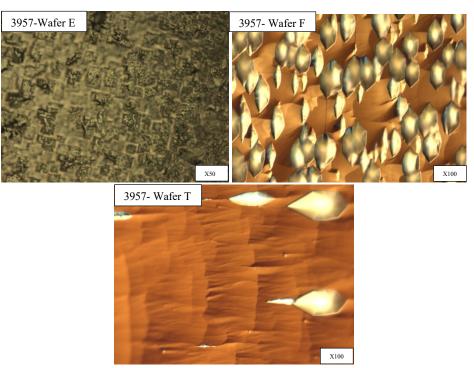

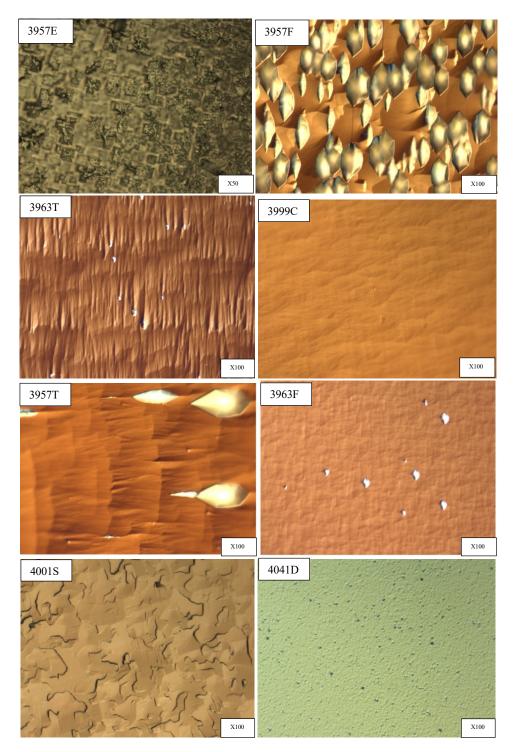

| Figure 3-5:  | Top view of Si substrate wafers in run 3957                                                               |    |

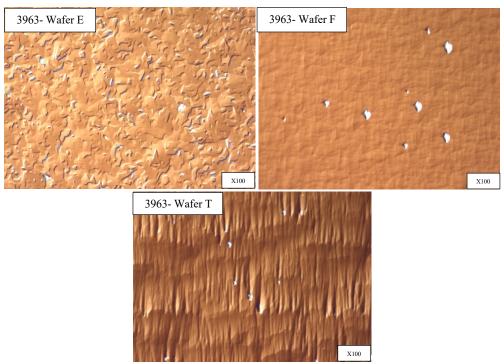

| Figure 3-6:  | Top view of Si substrate wafers in run 3963                                                               |    |

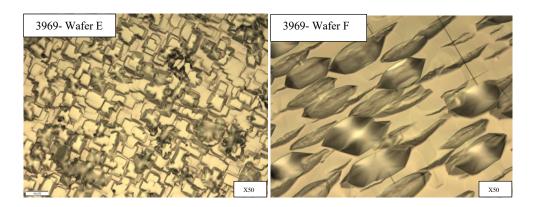

| Figure 3-7:  | Top view of Si substrate wafers in run 3969                                                               |    |

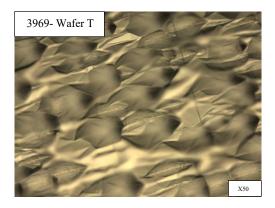

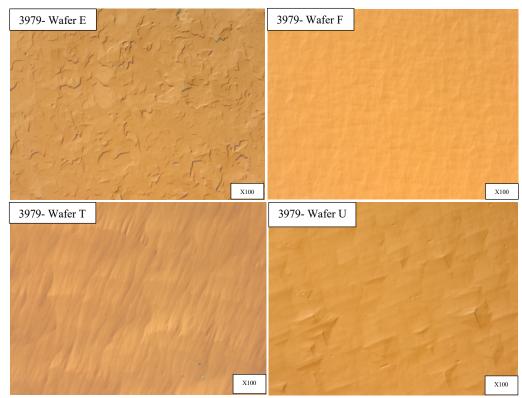

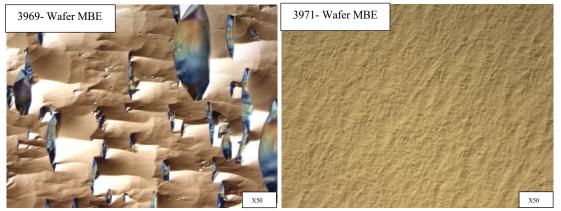

| Figure 3-8:  | Top view of Si substrate wafers in run 3971                                                               | 32 |

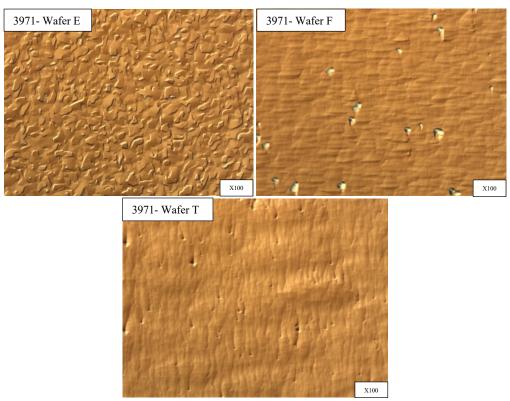

| Figure 3-9:  | Top view of Si substrate wafers in run 3979                                | 33 |

|--------------|----------------------------------------------------------------------------|----|

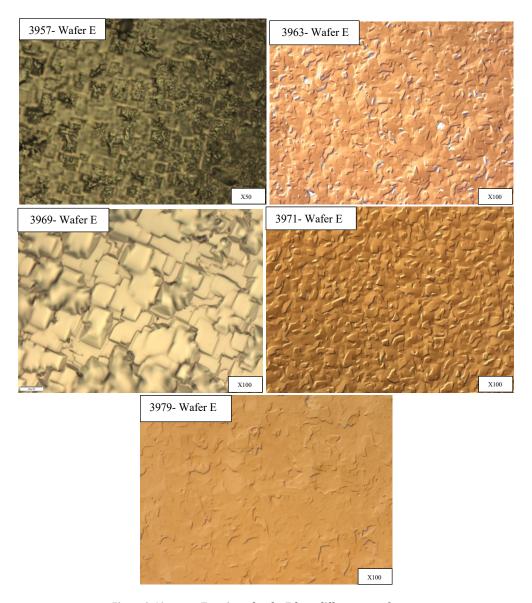

| Figure 3-10: | Top view of wafer E from different growth runs                             |    |

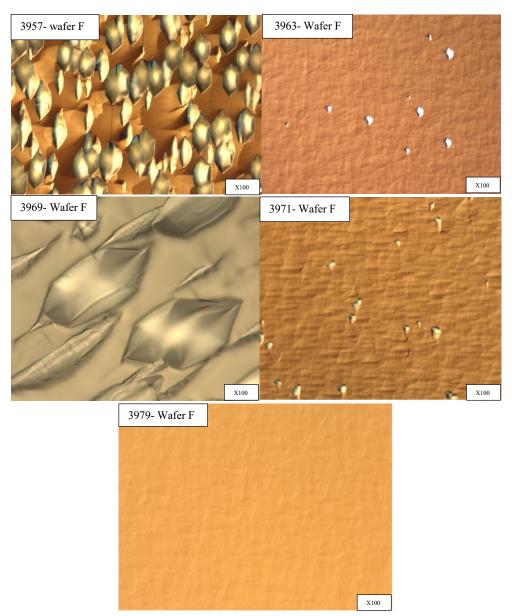

| Figure 3-11: | Top view of Wafer F from different growth runs                             | 35 |

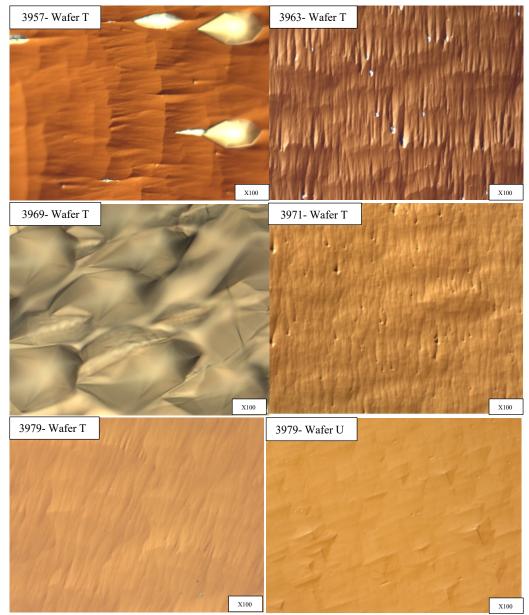

| Figure 3-12: | Top view of Wafer T from different runs and wafer U from run 3979          | 36 |

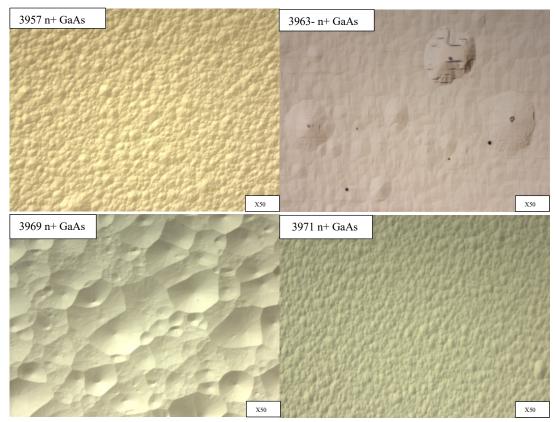

| Figure 3-13: | Top view of wafer n+ GaAs from different growth runs                       | 37 |

| Figure 3-14: | Top view of wafer MBE from different growth runs                           | 37 |

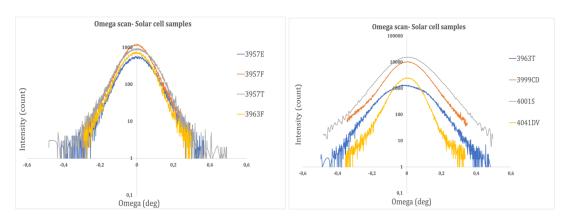

| Figure 4-1:  | Omega plots of solar cell samples                                          | 39 |

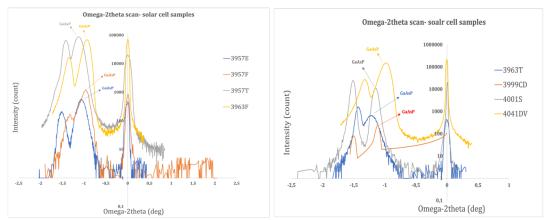

| Figure 4-2:  | Omega -2theta plots of sharp solar cell samples                            | 40 |

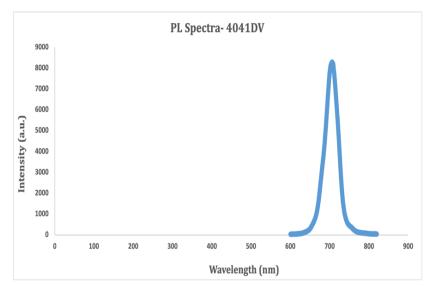

| Figure 4-3:  | Photoluminescence spectra of sample 4041DV, at middle of the sample,       |    |

|              | before dry III-V etching                                                   | 40 |

| Figure 4-4:  | Top view of solar cell samples                                             | 42 |

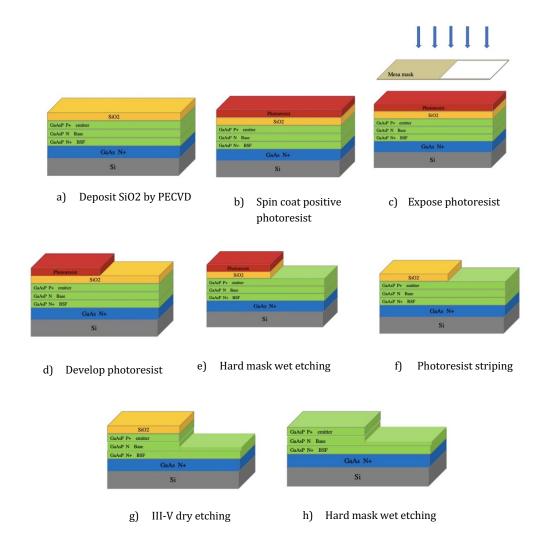

| Figure 5-1:  | Dry etching process flow for III-V semiconductors in the sharp samples     | 44 |

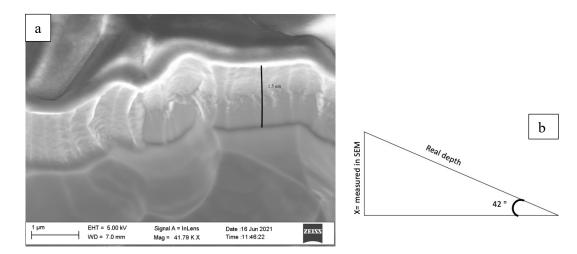

| Figure 5-2:  | a) SEM image of side wall of sample 3957E after dry III-V etching, b) real |    |

|              | depth calculation.                                                         | 47 |

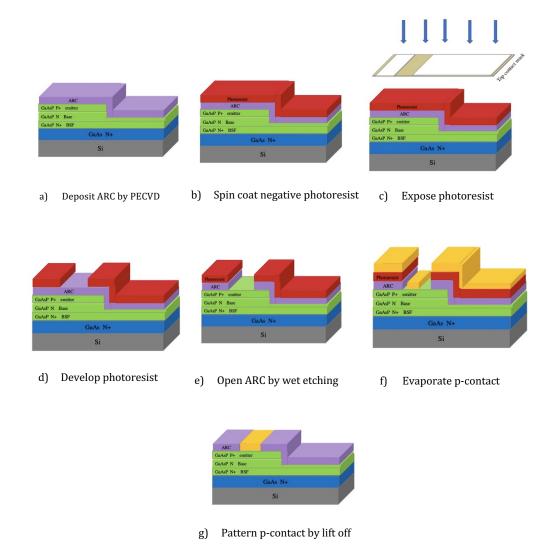

| Figure 5-3:  | P-contact formation                                                        | 48 |

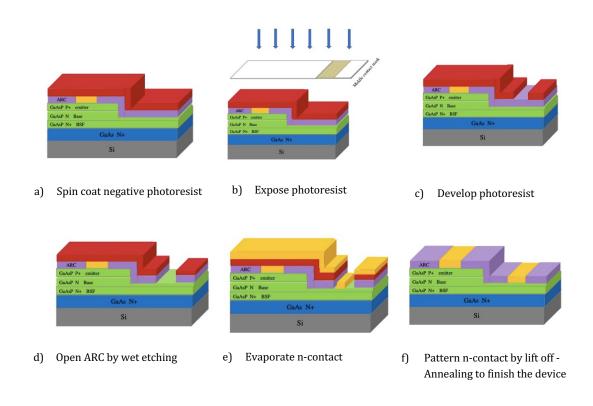

| Figure 5-4:  | N- contact formation                                                       | 50 |

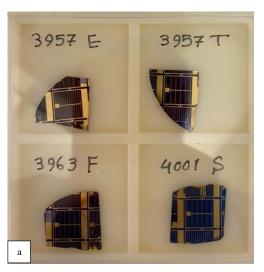

| Figure 6-1:  | Picture of fabricated Solar cell devices, b) picture of under processing   |    |

|              | solar cell device 4041DV (including Cell 1-Cell 8)                         | 52 |

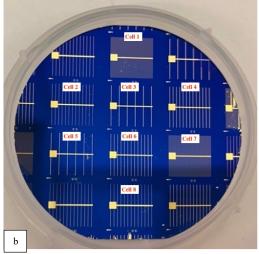

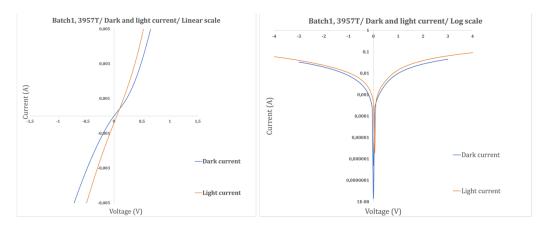

| Figure 6-2:  | Dark and light current curves of cell 3957E- batch 1, in linear and        |    |

|              | logarithmic scale.                                                         | 54 |

| Figure 6-3:  | Dark and light current curves of cell 3957T- batch 1, in linear and        |    |

|              | logarithmic scale.                                                         | 55 |

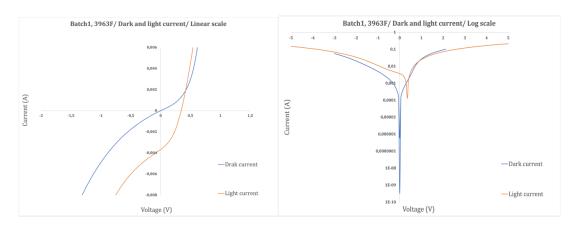

| Figure 6-4:  | Dark and light current curves of cell 3963F- batch 1, in linear and        |    |

|              | logarithmic scale                                                          | 55 |

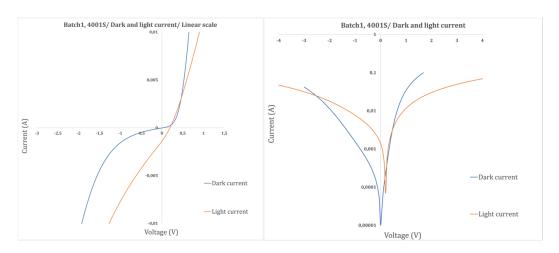

| Figure 6-5:  | Dark and light current curves of cell 4001S- batch1, in linear and         |    |

|              | logarithmic scale                                                          | 56 |

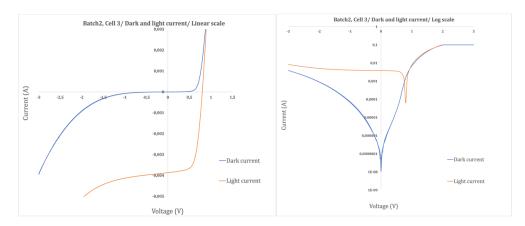

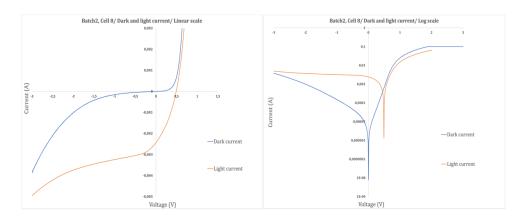

| Figure 6-6:  | Dark and light current curves of cell2- batch2, in linear and logarithmic  |    |

|              | scale                                                                      | 57 |

| Figure 6-7:  | Dark and light current curves of cell3- batch2, in linear and logarithmic  |    |

|              | scale                                                                      | 57 |

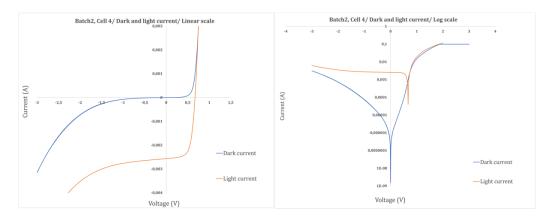

| Figure 6-8:  | Dark and light current curves of cell4- batch2, in linear and logarithmic  |    |

|              | scale                                                                      | 58 |

| Figure 6-9:  | Dark and light current curves of cell5- batch2, in linear and logarithmic  |    |

|              | scale                                                                      | 58 |

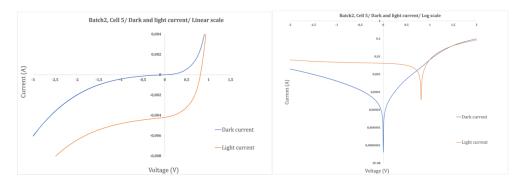

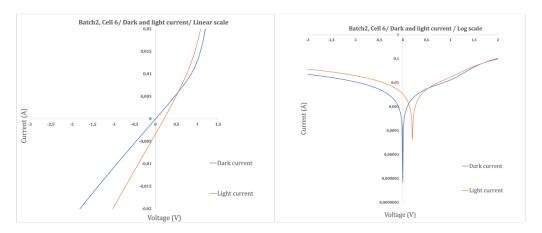

| Figure 6-10: | Dark and light current curves of cell6- batch2, in linear and logarithmic  |    |

|              | scale                                                                      | 59 |

| Figure 6-11: | Dark and light current curves of cell7- batch2, in linear and logarithmic  |    |

|              | scale                                                                      | 59 |

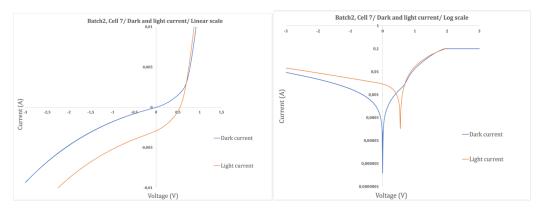

| Figure 6-12: | Dark and light current curves of cell8- batch2, in linear and logarithmic  |    |

|              | scale                                                                      | 60 |

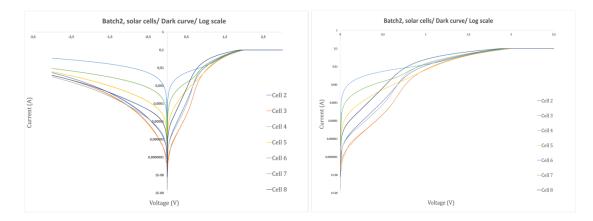

| Figure 6-13: | Dark curves of batch2 solar cells in logarithmic scale.                    | 61 |

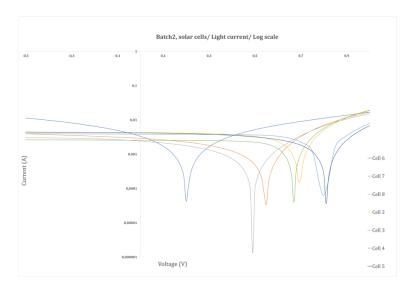

| Figure 6-14: | Light curves of batch2 solar cells in logarithmic scale                    | 61 |

# **List of Tables**

| Table 3.1: | information about samples grown for crystalline quality optimization   | 21 |

|------------|------------------------------------------------------------------------|----|

| Table 3.2: | Name of the samples in this thesis                                     | 22 |

| Table 3.3: | Growth conditions of sample grown for crystalline quality optimization | 22 |

| Table 3.4: | HRXRD results of grown samples for crystalline quality optimization    | 24 |

| Table 3.5: | FWHM values for different wafers of different runs                     |    |

| Table 3.6: | Optimized growth conditions.                                           | 38 |

| Table 4.1: | Information deduced from HRXRD measurement for the sharp solar cell    |    |

|            | samples                                                                | 39 |

| Table 4.2: | Information about PL characterization                                  | 41 |

| Table 5.1: | Thickness of SiO <sub>2</sub> layer deposited on samples               | 45 |

| Table 5.2: | Thickness of SiO <sub>2</sub> layer deposited on samples               | 45 |

| Table 5.3: | Exposure information on lithography procedure adopted for the sharp    |    |

|            | solar cell samples.                                                    | 45 |

| Table 5.4: | Information about wet etching of the SiO <sub>2</sub> hard mask        | 46 |

| Table 5.5: | Information about dry etching for III-V semiconductors                 | 46 |

| Table 5.6: | Information about deposition ARC for p-contact.                        | 49 |

| Table 5.7: | Information about wet etching the ARC for p-contact                    | 49 |

| Table 5.8: | Information about wet etching the ARC for n-contact                    | 51 |

| Table 6.1: | p-contact TLM measurement of solar cells.                              | 53 |

| Table 6.2: | n-contact TLM measurements of solar cells                              | 53 |

| Table 6.3: | Information deducted from light current curves of batch1 solar cells   | 56 |

| Table 6.4: | Information obtained from light curve of batch2 solar cells            | 60 |

| Table 6.5: | Power value for batch2 solar cells                                     | 62 |

# List of acronyms and abbreviations

Si silicon

GaAsP Gallium arsenide phosphide

GaAs Gallium arsenide

AsH<sub>3</sub> arsine

PH<sub>3</sub> phosphine

HRXRD High resolution x-ray diffraction

SEM Scanning electron microscopy

MOVPE Metal organic vapor phase epitaxy

CMP Chemical mechanical polishing

PECVD Plasma enhanced chemical vapor deposition

HVPE Hydride vapor phase epitaxy

ICP Inductively coupled plasma etching

TLM Transmission line method

FF Fill factor

BSF Back surface field

#### 1

#### 1 Introduction

Nowadays environmental problems caused by non-renewable energy sources have become a major issue around the world and investigating sustainable energies such as wind, sun etc., is inevitable. Sun is an essential source of renewable energy which is free and available widely in all parts of the earth and technology of using sunlight in industry has been improved significantly. The concept of photovoltaic effect was observed in 1839 for the first time and first solar cell was invented in 1883 [3] which was too inefficient. About seventy years later in 1954, first silicon (Si) solar cell was invented by researchers in Bell laboratory [4] that have been used widely around the world.

Traditional solar cells are fabricated of n-type and p-type Si to create a pn-junction and metal contacts on their top and bottom. Since only photons with energy higher than the bandgap of Si could be absorbed, the efficiency of single junction Si solar cell is so limited. Then many studies were done on III-V compound solar cells and their functionality. The materials used in III-V solar cells are compounds of elements of group III and V of the periodic table such as GaAs and GaAsP etc. Because of different bandgap energies, III-V solar cells absorb a broader range of solar spectrum and provide higher efficiency. However, due to their higher costs these have been exploited mainly in space applications and satellites and could not enter into terrestrial applications. Recently, scientists have been working on integrating III-V compound semiconductor on Si substrate to obtain high conversion efficiency at reasonably low price.

#### 1.1 Basic knowledge of solar cell

The basis of a solar cell functionality is founded by generation of the voltage and electrical current in a material caused by the exposure to the light, a phenomenon that is referred to as the photovoltaic effect. Electrons and holes are separated from each other by the inherent field existing at the pnjunction in a solar cell and therefore voltage and electrical current will be created. By putting a n-type next to a p-type semiconductor a pn-junction is created which is the building blocks of a solar cell.

In the absence of any external load, free electrons (holes) in n-type (p-type) diffuse into the p-type (n-type) which creates a depletion region close to the interface containing positive charges in n-type and negative charges in p-type.

This charge imbalance produces an electric field inside the depletion region from n-side to p-side. When a photon with energy ( $E = h\nu = \frac{hc}{\lambda}$ ) larger than the bandgap energy ( $E_g$ )of material shines on the material, it will excite electron in valence band and send it to conduction band and will leave a hole in valence band instead, this is called the absorption effect which creates electron-hole pairs.

When sunlight shines on solar cells, different wavelengths of photon are absorbed by pn-junction and electron-hole pairs are created. Electron goes to n-side (opposite side of electric field) and hole goes to p-side, as shown in yellow charges in Figure 1-1.

Now imagine there is a connection between metal contacts with wire, electrons will flow through the wire. Electrons are attracted to positive charges in p-type, so an electrical current will flow from p-side to n-side which is called photo current ( $I_{ph}$ ) and in the absence of any external load, photo current is called short circuit current ( $I_{SC}$ ). The potential between two metal contacts formed on p and n-sides, is called open circuit voltage ( $V_{OC}$ ).

Figure 1-1: Cross section of a solar cell at zero bias, where ARC means Anti Reflection Coating.

When a solar cell contains only one pn-junction it is called a single-junction solar cell whereas multijunction solar cell is a cell with more than one pn-junction made of several semiconductor materials of different bandgaps.

The efficiency of a solar cell is the most important feature of it and could be defined as amount of electric power  $(P = I \times V)$  coming out of the cell compared to energy from the shining light on the cell. Undoubtedly solar cells with higher efficiency are desired.

In a single-junction solar cell, e.g., conventional Si solar cell of 1.1[ev] bandgap, the maximum efficiency that can be obtained by using the spectrum of light having higher energy than that of the bandgap of semiconductor material is limited to 30%, a constraint that is referred to as the Shockly-Queisser limit [5]. To overcome this limitation and use the absorption of a broader spectrum of light, we can use different semiconductor materials on top of each other and accordingly generate more electrical current.

Multiple semiconductor materials would have multiple bandgaps which response to variety of light wavelengths. Since the photon energy should be larger than the bandgap of the semiconductor material to be able to create electron-hole pairs, high energy photon which has lower wavelength will be absorbed by a larger bandgap material and photon with higher wavelength will be absorbed by lower bandgap material. Therefore, multi-junction solar cells can absorb a broader range of light wavelengths and convert it to electricity.

In designing multi-junction solar cells, material with larger bandgap is integrated on top along with the material with the lower bandgap at the bottom. This configuration allows higher energy photons to be absorbed by the top material and low energy photons by the bottom material. Figure 1-2 shows the solar spectrum absorbed by a multi-junction solar cell. In this case, the top cell consisting of InGaP with bandgap of 1.86 eV absorbs wavelength less than 800 nm and the bottom cell consisting of Ge with bandgap of 0.65 eV absorbs wavelength between 1100 nm and 1800 nm.

Figure 1-2: Multiple layers of multi-junction solar cell absorbing specific range of Air mass 1.5 solar spectrum [6].

In conclusion, multi-junction solar cells are more efficient at converting sunlight to electricity compared to the single-junction solar cells. A single-junction solar cell with non-concentrated sunlight has efficiency about 33.5% [7], whereas the efficiency for a multi-junction cell is over 46% [8].

By increasing the number of pn-junctions a broader spectrum can be absorbed, and the efficiency of the solar cell will increase. Figure 1-3 shows a relation between number of pn-junctions and the projected efficiency, that could be a theoretical projection.

Figure 1-3: Relation between number of pn-junctions in solar cell and the efficiency of it [9].

Tandem solar cell is a type of multi-junction solar cell which two or more pn-junctions are on top of each other. Basic designs of tandem solar cells are either by growing layers on top of a substrate which is called monolithic or by stacking devices mechanically, e.g., by bonding. Choosing suitable semiconductor materials for tandem solar cells could be a challenge and here are some factors to be

considered. For example, bandgaps of materials should be matched with the spectrum and crystal lattice constants must be the same to avoid crystalline defects.

III-V compounds have wide range of bandgaps and hence are amenable for combining to create tandem solar cells to match specific solar spectrum with specific bandgap. Therefore, III-V semiconductors have been used in multi-junction solar cells showing high conversion efficiency.

The most application of III-V solar cells are in space and satellites due to their high conversion efficiency and better radiation resistance.

Even though III-V semiconductor multijunction solar cells are the most efficient solar cells, they are expensive due to the high cost of the fabrication techniques and materials. Typically, GaAs or Ge are used as substrate in III-V multi junction solar cells which are expensive. Nonetheless Si can be used as a substrate which could lower the costs to some extent.

In this work, compound semiconductor material,  $GaAs_xP_{1-x}$  is used as the material to absorb light on GaAs/Si substrate and design of the solar cell devices in this project is shown in Figure 1-4. However, the p-contact mask used in this project contains three different patterns in terms of distance between contact fingers which might have effect on the performance of the cells.

Figure 1-4: Top view of a fabricated solar cell device in this project.

To investigate the functionality of the solar cell device, two kinds of measurements are usually performed, TLM measurement and IV characterization, which will be discussed later.

#### 1.2 Objective of the thesis

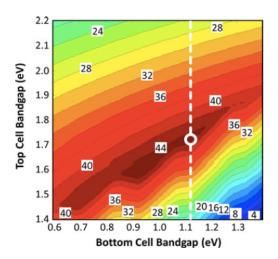

According to Figure 1-5, for Si bottom cell with bandgap 1.1[ev], the ideal top cell bandgap value is 1.7ev. Therefore, we aim for  $GaAs_{0.75}P_{0.25}$  in this project.

However, in experiment we managed to fabricate and characterize  $GaAs_{0.74}P_{0.26}/GaAs/Si$  solar cell. This is a main building block towards the final goal of fabricating a tandem multijunction solar cell.

Figure 1-5: Detailed balance efficiency for dual junction series-connected solar cell under 1-sun AM1.5G. [10]

Metal contacts are formed on the sample through different steps in fabrication process and at the end performance of the fabricated devices is investigated.

The schematic form of initial sample and fabricated solar cell in this work is shown in Figure 1-6.

Figure 1-6: Cross section of initial sample (left) and solar cell device (right).

Basically, the thesis is about the fabrication of  $GaAs_xP_{1-x}$  solar cell on GaAs coated Si substrate where the  $GaAs_xP_{1-x}$  epitaxial layer is grown under different growth conditions on top of different kinds of GaAs/Si substrates. Therefore, the objective of the thesis is:

- 1. Investigation of crystal quality of the  $GaAs_xP_{1-x}$  epitaxial layer grown on different kinds of GaAs/Si substrates by characterizing it to obtain the optimized growth conditions and finding the best substrate.

- 2. Fabrication of  $GaAs_{0.75}P_{0.25}$  solar cell on GaAs coated Si substrate.

- 3. Investigation and comparing the performance of fabricated solar cells.

In addition to chapter 1 which is introduction, there are 6 other chapters. Contents of these 6 chapters are as follow:

In chapter 2, scientific theory of experimental methods and tools that are used in this project are discussed. Chapter 3 describes the process of optimizing the crystal quality of the grown epitaxial layer. In chapter 4, samples chosen for the solar cell fabrication are characterized and relative results reported. Chapter 5 describes the fabrication process, step by step. Chapter 6 is about device characterization to assess the performance of fabricated solar cells. Chapter 7 gives a general conclusion and some suggestions for future works.

### 2 Experimental set up

#### 2.1 Low pressure Hydride Vapor Phase Epitaxy (LP-HVPE)

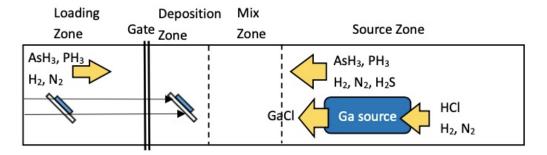

HVPE is an epitaxial growth method to prepare low cost, high efficiency III-V solar cells. In this work  $GaAs_xP_{1-x}$  layers are grown on on-axis and off cut GaAs (001) and Si (001) substrates. In HVPE reactor, group V precursors which are arsine (AsH<sub>3</sub>), and phosphine (PH<sub>3</sub>) are used to produce As and P, respectively. The other precursor is GaCl which is generated by the reaction between HCl and molten Ga.

$$2Ga(l) + 2HCl(g) \rightarrow 2GaCl(g) + H_2(g)$$

And the growth reaction to get  $GaAs_xP_{1-x}$  can be written as below:

$$xAsH_{3}(g) + GaCl(g) + (1-x)PH_{3}(c) \rightarrow GaAs_{x}P_{1-x}(s) + HCl(g) + H_{2}(g)$$

In HVPE reactor, first GaCl is generated by the reaction between HCl and melted Ga and then GaCl will be mixed with group V gases such as arsine and phosphine to produce  $GaAs_xP_{1-x}$  that is deposited on GaAs/Si substrate.

Desired  $GaAs_xP_{1-x}$  composition can be achieved by changing the flow of arsine and phosphine in the reactor. The strength of HVPE technique can be mentioned in two aspects: high growth rate can be achieved by HVPE since the growth rate is determined by mass input rate of reactants [11]. Moreover, by changing the gas phase components one can get desired composition. To be able to deposit III-V semiconductors in large scale, it is essential to decrease the epitaxial cost. Since HVPE reactor uses low-cost elemental source materials and produces a high quality III-V growth, so epitaxial growth using HVPE is more reasonable compared to metal organic vapor phase epitaxy (MOVPE) which is more expensive.

Figure 2-1: Schematic form of HVPE reactor [11]

In this work, samples are grown using HVPE reactor in Electrum Lab and are schematically shown in Figure 2-1.

#### 2.2 Characterization methods

#### 2.2.1 High Resolution X-Ray Diffraction (HRXRD)

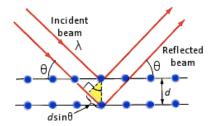

HRXRD is a popular characterization tool to study the crystalline quality, composition, thickness (in certain cases), etc. of a sample. Consider parallel planes of atoms with space "d", constructive interference occurs when Bragg's law is satisfied.

$$2d \sin \theta = n\lambda$$

where,  $\theta$  is the incident angle,  $\lambda$  is the wavelength of incident radiation and n is the diffraction order (an integer). When an incident beam strikes a crystal plane, reflected beams will interfere constructively and have maximum intensity only if the incident angle satisfied Bragg's law. Figure 2-2 shows schematic form of Bragg's law.

Figure 2-2: Schematic form of Bragg's law [12]

In HRXRD tool, X-Ray beam is produced by X-Ray tube (source) shown at the left side of Figure 2-3. Then the produced X-Ray passes through a monochromator and strikes the crystal placed on sample stage at angle  $\omega$  and then are diffracted and collected by X-ray detector at angle 20.

Sample stage can be tilted in  $\omega$ ,  $\varphi$ ,  $\psi$  angles and move along z direction. To get the maximum intensity, these directions need to be optimized before doing the real measurement.

Figure 2-3: Schematic form of HRXRD tool [13].

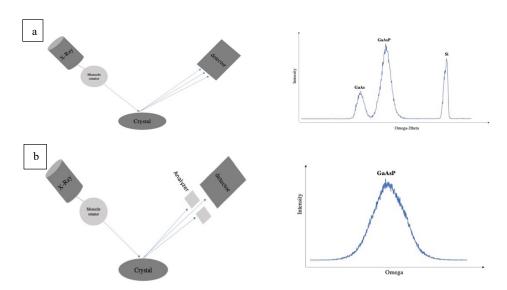

Two configurations are used for HRXRD measurement, double axis, and triple axis. In the rocking curves collected on double axis, detector can collect different angles, so all the peaks can be observed and is called  $\omega$ -20 (omega-2theta). In this project,  $\omega$ -20 scan in double axis has been used to see three possible peaks of GaAs<sub>x</sub>P<sub>1-x</sub>/GaAs/Si samples and deduct information about composition of the grown layer. The composition of the epitaxial layer is calculated from separation between layer peak and substrate peak in Omega-2theta scan where substrate peak (Si) is reference. For instance, in Figure 2.4 (a-right) the right peak is Si peak considered as reference and the GaAs peak on the left show "x" value

in  $GaAs_xP_{1-x}$ . Therefore, the composition of the epitaxial layer can be determined easily and should be confirmed by PL measurement later.

In rocking curve on triple axis, the analyzer constrains detector, so only one  $2\theta$  angle can be collected. In this project, an Omega scan on  $GaAs_xP_{1-x}$  layer is done in triple axis. In  $\omega$  scan, intensity versus  $\omega$  is plotted and any defect in the crystal makes the curve wider, so the wider FWHM value shows the worse crystalline quality.

Figure 2-4 shows HRXRD configurations and produced plot using these configurations in this project.

Figure 2-4: Configuration of HRXRD in double axis (a) and in triple axis (b) and their application in the thesis.

In this project most samples are characterized by high resolution XRD tool that has both double axis and triple axis. A few samples are also characterized by other tool that has only double axis, but by limiting the number of pixels used in the detector, 2Theta range is limited and the resolution is acceptable for the samples.

HRXRD characterization results are reported in the next chapters.

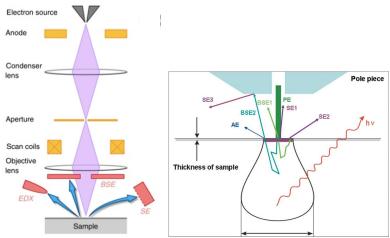

#### 2.2.2 Scanning Electron Microscopy (SEM)

Scanning electron microscope is a kind of microscope using electron beams to scan the surface of sample. Scientists can observe the structure with higher resolution and better depth of field compared to optical microscope in micrometer level. SEM configuration consists of different parts such as electron source, lenses, and aperture. Electron beams generated by electron source (or electron gun) are focused by condenser lens, then passe through the aperture and scan coils, then primary electron beam is formed. This primary electron beam reaches the sample and interacts with surface of the sample. Interaction of electron beams with sample surface generates beams such as secondary electrons (SE), back scattered electrons (BSE), etc. The detector positioned above the sample collects the generated beams and the result will be shown on the screen.

Figure 2-5: (Left) Structure of scanning electron microscope (SEM) [14], (right) generation of various electrons in SEM [15].

As was mentioned above different types of electrons are generated because of interaction between primary electron and sample surface. In general, secondary electrons (SE) are generated at shallow depths in the sample whereas back scattered electrons (BSE) are generated from deeper depths in the sample and can provide better information as can be seen in Figure 2-5 (right).

In this thesis Gemeni- Ultra 55 manufactured by Zeiss is used to observe and measure cross section and the depth of some dry-etched III-V samples and InLens mode was used in measurements.

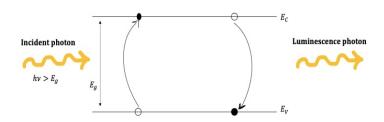

#### 2.2.3 Photoluminescence spectroscopy (PL)

PL is a characterization method in which crystalline quality and the bandgap of the semiconductor materials are investigated. The latter can yield the composition of the material. When a photon with energy higher than bandgap energy of material strikes the material, electrons in valence band get photon's energy and jump to conduction band, this effect is called absorption which is shown in Figure 2-6 (left). After a while these stimulated electrons relax and get back to valence band, releasing the energy as light, which is shown in Figure 2-6 (right). The emission light is detected in PL tool and gives information about the bandgap of the semiconductor material.

Figure 2-6: (Left) Absorption and electron excitement, (right) light emission.

PL is complementary to HRXRD technique to identify the composition of the studied  $GaAs_xP_{1-x}$  layer. Since the bandgap  $E_g$  of  $Ga_xAs_{1-x}P=f$  (a, x,) where a is the lattice constant and x, the composition, knowing a from HRXRD and  $E_g$  from PL, x can be calculated.

#### 2.2.4 Transmission Line Method (TLM)

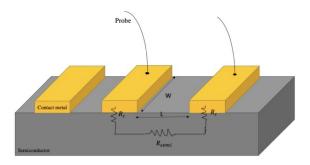

Once a solar cell device is fabricated, important parameters such as specific contact resistance between metal and semiconductor as well as sheet resistance should be measured and TLM is a method to measure such parameters.

By applying a voltage across the contacts and knowing the current flow through the device, one can calculate the resistance of the metal contacts.

Two probe measurement stations are used for TLM measurement in this project. Consider two metal contacts with distance "L" apart from each other in TLM pattern of the device as shown in Figure 2-7. Electrical current flows from one probe to a metal contact, passes contact-semiconductor interface, goes through the semiconductor sheet, passes contact-semiconductor interface again and goes to the second metal contact.

Figure 2-7: Schematic form of the TLM pattern of a solar cell.

The total resistance ( $R_T$ ) includes the semiconductor resistance ( $R_{semi}$ ) and two contact-semiconductor resistances ( $R_C$ ).

$$R_T = R_{semi} + 2R_C$$

[1]

Semiconductor resistance is  $R_{semi} = \rho \frac{L}{A} = \rho \frac{L}{W \times thickness}$

[2], where  $\rho$  is the resistivity.

[3]

Since the sheet resistance is defined as  $R_{sheet} = \frac{\rho}{thickness}$

total resistance can be written as below:

$$R_T = \frac{L}{W} R_{sheet} + 2R_C \quad [4]$$

By knowing the L values from photomask or measured on optical microscope and total resistance measured by two probe stations, total resistance as a function of contact spacing is obtained.

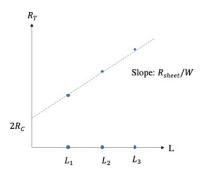

Total resistance as a function of contact spacing can be plotted as shown in Figure 2-8.

Figure 2-8 Plot of total resistance of the device vs contact distances.

The slope of the graph is  $\frac{R_{sheet}}{W}$ , which can be calculated from the plot.

However, since the current does not flow in the contact uniformly, the physical geometry of contact cannot be used to determine the contact area and that brings us to the concept of transfer length.

Transfer length is the average distance that electron travels in semiconductor under the metal contact before reaching the contact and is defined as  $L_T = \sqrt{\frac{r_c}{R_{sheet}}}$  [ $\mu m$ ] [6],

where  $r_c$  is specific contact resistance, given as  $r_c = R_c$ . A  $[\Omega.cm^2]$

For the cases that  $L_T$  is very small compared to contact pad dimensions, the effective area of the contact can be calculated as  $WL_T$ .

Therefore, total resistance can be written as below:

$$R_T = \frac{R_{sheet}}{W} (L + 2L_T)$$

[7]

In this project, TLM measurement is performed for solar cell devices and parameters such as sheet resistance, specific contact resistance as well as transfer length and contact resistance are obtained.

#### 2.2.5 IV characterization

Investigation of current- voltage (IV) relation of a solar cell provides information about the functionality of the device. Two kinds of IV measurement are usually performed, dark current and light current.

#### Dark current curve:

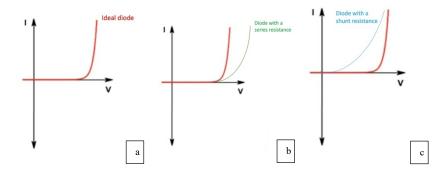

Solar cell in the absence of light works like a diode, therefore checking the dark current curve is a method to check the functionality of the pn-junction of the solar cell. By applying a positive voltage to p-side and negative voltage to n-side, pn-junction is under forward bias, and current is allowed to pass through the junction. The relation between applied voltage and generated current is shown in an IV curve called dark current curve.

In the absence of light, solar cell works like an ideal diode, but if the IV curve of a solar cell does not look like the IV curve of an ideal diode, there are three possible cases:

- 1. If there is a deviation at higher current, it indicates a series resistance with pn-junction.

- 2. If there is a hump at lower current, it shows a parallel (shunt) resistance with pn-junction.

- 3. If there are both deviations at higher current and hump at lower current indicates both series and shunt resistance.

Dark current curves of a solar cell in linear scale are shown in Figure 2-9.

Figure 2-9: Dark current curve of an ideal diode (a), diode with a series resistance (b) and diode with a shunt resistance (c) in linear scale.

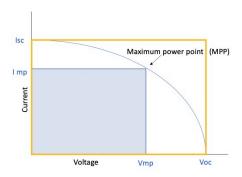

#### Light current curve:

Air-mass (AM1.5) spectrum is a global spectrum which simulates sunlight and has been used to test photovoltaic devices. In this work also, solar cells have been exposed by AM1.5 spectrum to be tested and characterized and result is reported as light current curve.

When the device is characterized under standard spectrum (AM1.5), in the absence of any external voltage, a current is generated flowing through the device which is called photo current ( $I_{ph}$ ) which is short circuit current but in reverse direction ( $I_{ph} = -I_{SC}$ ). The relation between current and voltage of the solar cell is presented in light current curve in the first quadrant as shown in Figure 2-10. Key parameters are deduced from light current curve such as efficiency of the cell which could be defined as amount of electric power ( $P = I \times V$ ) coming out of the cell compared to energy from the shining light on the cell. The other important parameter is fill factor (FF) which is a measure of quality of solar cell and is calculated as below,

$$FF = \frac{P_{max}}{P} = \frac{I_{mp} \times V_{mp}}{I_{SC} \times V_{OC}}$$

Where  $I_{mp}$  and  $V_{mp}$  are current and voltage of the maximum power, respectively.

As it can be seen in Figure 2-10, the interception of light current curve with x and y axis are  $V_{OC}$  and  $I_{SC}$ , respectively.

The area of blue rectangular is maximum power ( $P_{max} = I_{mp} \times V_{mp}$ ) that solar cell can provide and the area of yellow rectangular is solar cell power ( $P = I_{SC} \times V_{OC}$ ).

The larger number of FF indicates the better quality of solar cell. The light current curve of a solar cell as well as maximum power point are shown in Figure 2-10.

Figure 2-10 Light current curve of a solar cell in log scale.

The schematic form of solar cell in absence of light and corresponding dark current curve (a) and also under standard spectrum (AM1.5) and corresponding light current curve (b) are shown in Figure 2-11.

Figure 2-11: PN junction of a solar cell in darkness (a) pn- junction of solar cell under illumination (b) and corresponding IV curves in linear scale.

In this project for each fabricated solar cell a dark and light curve is plotted in linear and log scale to interpret the functionality of the device.

In light current curve in linear scale the intersection of the curve with voltage axis and current axis shows open circuit voltage ( $V_{OC}$ ) and short circuit current ( $I_{SC}$ ), respectively, as it is shown in Figure 2-12 (left).

In light current curve in log scale the minimum point of the plot shows open circuit voltage ( $V_{OC}$ ) and intersection of the plot with current axis shows short circuit current ( $I_{SC}$ ), as you can see in Figure 2-12 (right).

Figure 2-12: Dark and light current curve of a solar cell in linear scale (left) and in log scale (right).

#### 2.3 Fabrication tools

During the fabrication process of the solar cells number of tools in cleanroom have been used and here the operating principles of the most important ones is described.

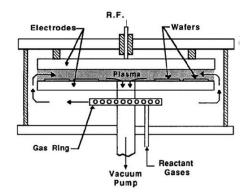

#### 2.3.1 Plasma Enhanced Chemical Vapor Deposition (PECVD)

PECVD is a chemical deposition method to deposit thin film such as silicon dioxide ( $SiO_2$ ) or silicon nitride ( $Si_3N_4$ ) on a substrate. In PECVD, thin film is deposited uniformly all over the substrate and the process occurs at temperature of 300°C. The tool consists of two electrodes parallel to each other and a substrate is placed on one electrode. Reactant gaseous such as  $SiH_4$ ,  $NH_3$ ,  $N_2O$ , etc. are introduced to the space between two electrodes, just above the substrate. When reactant gaseous are ionized, plasma is generated. Then the generated plasma will react chemically with the substrate and thin film is deposited. Figure 2-13 shows schematic form of PECVD.

Chemical reaction to produce SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> can be written as below.

$$SiH_4 + 2N_2O \rightarrow SiO_2 + 2N_2 + 2H_2$$

$3SiH_4 + 4NH_3 \rightarrow Si_3N_4 + 12H_2$

Figure 2-13: Schematic form of PECVD [16].

In this thesis, Plasma lab 80Plus (Oxford PECVD System) chamber A, is used to deposit silicon dioxide  $(SiO_2)$  as hard mask for mesa etching and silicon nitride ( $Si_3N_4$ ) as anti-reflection coating (ARC) on samples. The information about depositions will be discussed later.

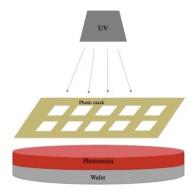

#### 2.3.2 Photolithography

Photolithography is one of the most used techniques to pattern a wafer with the help of a designed photo mask. In this method wafer is covered by a photoresist (resist) and will be exposed by light through the mask to replicate its pattern.

There are two types of the resist, positive and negative. When exposure is performed there will be a chemical reaction in positive resist and exposed part of resist will be removed by a developer whereas in negative resist unexposed parts will be removed.

As figure 2-14 shows, a photo mask is placed at a specific distance called alignment gap (AG) above the wafer. First alignment needs to be done by moving the wafer stage to transfer the pattern on the right position on the wafer. Light source is above the mask and during the exposure, light will shine through the mask into the wafer.

Figure 2-14: Schematic form of Photolithography.

After exposure for a desired time, resist will be removed by a developer and the desired pattern can be seen on the wafer. After that, possible residual resist will be removed by plasma treatment in an equipment called Tepla.

In this project tool Mask aligner MA6/BA6 Karl Suss is used which has UV light as source. In addition, in mesa patterning positive resist and in top and middle contact patterning negative resist are used.

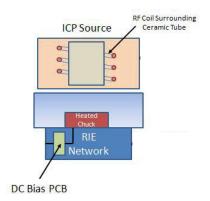

#### 2.3.3 Inductively Coupled Plasma Etching (ICP)

ICP which is also called dry plasma etching is a technique using plasma to etch III-V semiconductors.

Gases are introduced above an inductive coil and sample is placed on a chuck. Radio frequency (RF) is applied to coil and the chuck to create plasma. By introducing gases such as Argon (Ar) chemical reactions take place which generate plasma.

Figure 2-15 shows an ICP tool schematically.

Figure 2-15: Schematic form of ICP [17].

The advantage of using plasma in dry etching is having control of etch profile, which does not happen in wet etching. The profile in this technique is usually anisotropic.

In this project Oxford Instrument ICP380 Etch System has been used to etch GaAsP layer with an etch rate around 0.7  $\mu$ m/min. Information about dry etching of the samples will be discussed in detail in next chapters.

#### 2.3.4 Metal evaporation

Metallization is the final step in the fabrication of solar cell devices in which a thin layer of desired metal(s) is(are) deposited on device to collect the photo generated current.

In this project, first through different process steps, p-contact is implemented. For this, a P-type semiconductor (GaAsP) and metal (Cr/Au) Junction is created. Then N-contact is implemented. For this a N-type semiconductor (GaAsP) and metal (Au/Ge/Ni/Au) junction is created.

When a metal is in contact with a wide bandgap semiconductor (such as III-V) results in a Schottky contact, but since the electrical current needs to flow into and out of the semiconductor, an ohmic contact should be created. To create an ohmic contact, a highly doped semiconductor is placed in contact with metal.

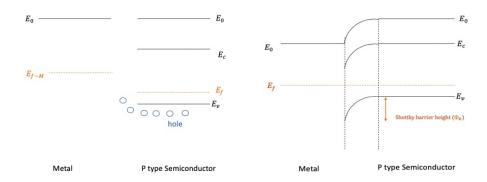

#### P- type Schottky junction:

To form a P-type Schottky junction (barrier), the distance between vacuum and fermi level (work function) of metal is less than the work function of semiconductor. When a metal is in contact to P-type semiconductor, their vacuum levels ( $E_0$ ) are aligned to each other as it is shown in Figure 2-16 (left). Since holes like to go up a slope which means higher energy, they go from valence band of P-type semiconductor up to metal easily. Therefore, due to depletion of holes, the fermi level of P-type semiconductor goes up and aligns with fermi level of metal. As it is shown in Figure 2-16 (right), the magnitude of the potential is "Schottky barrier height"

Figure 2-16: Energy band diagram of metal and P-type semiconductor Schottky junction before (left) and after (right) equilibrium.

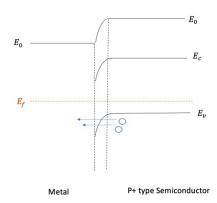

#### P- type Ohmic junction:

To form a P-type ohmic junction, one way is to dope the semiconductor highly to get tunneling. When the semiconductor is highly doped, the barrier will be very thin and charge carriers (in this case holes) could tunnel through the barrier.

Since P-type GaAsP is highly doped, instead of overcoming the barrier holes could tunnel through the barrier between metal to P+ type semiconductor. Therefore, an ohmic junction is created.

Figure 2-17 shows energy band diagram of a P-type Ohmic junction.

Figure 2-17: Energy band diagram of metal and P-type Ohmic junction, tunnelling effect.

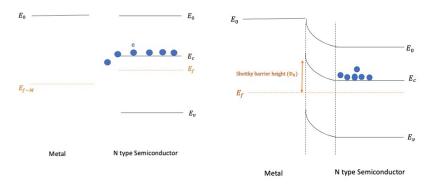

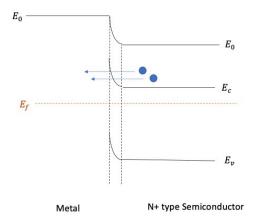

#### N- type Schottky junction:

To form a N-type Schottky junction (barrier), the distance between vacuum and fermi level (work function) of metal is more than the work function of semiconductor.

When a metal is in contact to N-type semiconductor, their vacuum levels ( $E_0$ ) are aligned to each other as it is shown in Figure 2-18 (left). Since electrons like to go down slope which means lower energy, they go from conduction band of N-type semiconductor come down to metal easily. Therefore, there will be lack of electrons in semiconductor, so its fermi level will go down and align with fermi level of metal and therefore conduction band, valence band and vacuum level would also go down, Figure 2-18 (right). The vacuum levels must be in the same, so they are connected as Figure 2-18 (right) shows and this is how a barrier is created.

Figure 2-18: Energy band diagram of metal and a N-type semiconductor Schottky junction before (left) and after (right) equilibrium.

#### N- type ohmic junction:

To form a N-type ohmic junction, one way is to dope the semiconductor heavily to get tunneling. When the semiconductor is highly doped, the barrier will be very thin and charge carriers (in this case electrons) could tunnel through the barrier.

Adding Ge (germanium) to metals would locally enhance the doping of the semiconductor and electrons could tunnel through barrier between metal and n+ type semiconductor. Therefore, an ohmic contact is created.

Figure 2-19 shows N-type Ohmic junction.

Figure 2-19: Energy band diagram of a N-type ohmic junction.

In this project, the contact between metals (Cr and Au) and p-type GaAsP (p-contact) as well as the contact between metals (Au/Ge/Ni/Au) and n-type GaAsP (n-contact) need to be ohmic with low resistance.

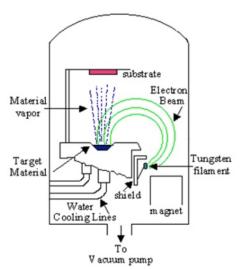

Metals in p and n-contact are deposited by e-beam evaporation, shown in Figure 2-20. In this method an energetic electron beam is generated from a filament and is conducted to source material (Au, Ni) by magnetic field and vaporize it. Samples are placed on a stage facing down on top of the chamber and the stage is rotating very slowly to deposit the metals homogeneously on samples.

Figure 2-20: Schematic form of metal evaporation tool [18].

In this thesis Provac PAK 600 Coating System has been used to deposit metals as below: For p-contact Cr 40nm/ Au 180nm are deposited and for n-contact Au 100nm (bottom layer)/ Ge 50nm/ Ni 50nm/ Au 100nm (top layer) is deposited. However, the thickness of top layer Au for one sample increased to 600nm. Results and information about metallization will be discussed in the next chapters.

# 3 Crystal quality optimization

#### 3.1 Growth conditions

Growth conditions such as temperature and precursor flows could affect the crystalline quality of the epitaxial layer. To fabricate a decent solar cell device out of a sample,  $GaAs_xP_{1-x}$  layer from which solar cell structure is based on, should be grown under an optimized growth condition. Therefore, by investigating the crystalline quality of the grown  $GaAs_xP_{1-x}$  layer and finding the best result, one can obtain the optimized growth conditions. Information about  $GaAs_xP_{1-x}$  samples grown in HVPE including run number and kind of substrate is presented in Table 3.1.

| Run number | Sample                                                                      |

|------------|-----------------------------------------------------------------------------|

|            | GaAs <sub>x</sub> P <sub>1-x</sub> / GaAs on On-axis Si substrate           |

| 3957       | GaAs <sub>x</sub> P <sub>1-x</sub> / GaAs on Off-cut Si substrate           |

|            | GaAs <sub>x</sub> P <sub>1-x</sub> / thickened GaAs on off-cut Si substrate |

|            | GaAs <sub>x</sub> P <sub>1-x</sub> / n+ GaAs substrate                      |

|            | GaAs <sub>x</sub> P <sub>1-x</sub> / GaAs on On-axis Si substrate           |

| 3963       | GaAs <sub>x</sub> P <sub>1-x</sub> / GaAs on Off-cut Si substrate           |

|            | GaAs <sub>x</sub> P <sub>1-x</sub> / thickened GaAs on Off-cut Si substrate |

|            | GaAs <sub>x</sub> P <sub>1-x</sub> / n+ GaAs substrate                      |

|            | GaAs <sub>x</sub> P <sub>1-x</sub> / GaAs on On-axis Si substrate           |

|            | GaAs <sub>x</sub> P <sub>1-x</sub> / GaAs on Off-cut Si substrate           |

| 3969       | GaAs <sub>x</sub> P <sub>1-x</sub> / thickened GaAs on Off-cut Si substrate |

|            | GaAs <sub>x</sub> P <sub>1-x</sub> / GaP on Si substrate                    |

|            | GaAs <sub>x</sub> P <sub>1-x</sub> / n+ GaAs substrate                      |

|            | GaAs <sub>x</sub> P <sub>1-x</sub> / GaAs on On-axis Si substrate           |

|            | GaAs <sub>x</sub> P <sub>1-x</sub> / GaAs on Off-cut Si substrate           |

| 3971       | GaAs <sub>x</sub> P <sub>1-x</sub> / thickened GaAs on Off-cut Si substrate |

|            | GaAs <sub>x</sub> P <sub>1-x</sub> / GaP on Si substrate                    |

|            | GaAs <sub>x</sub> P <sub>1-x</sub> / n+ GaAs substrate                      |

|            | GaAs <sub>x</sub> P <sub>1-x</sub> / GaAs on On-axis Si substrate           |

|            | GaAs <sub>x</sub> P <sub>1-x</sub> / GaAs on Off-cut Si substrate           |

| 3979       | GaAs <sub>x</sub> P <sub>1-x</sub> / thickened GaAs on Off-cut Si substrate |

|            | $GaAs_xP_{1-x}$ / thickened $GaAs$ on polished Off-cut Si substrate         |

|            | GaAs <sub>x</sub> P <sub>1-x</sub> / n+ GaAs substrate                      |

Table 3.1: information about samples grown for crystalline quality optimization.

Since in each run  $GaAs_xP_{1-x}$  has been grown on different substrates, in this thesis samples are named as E, F, T, MBE and n+ GaAs to be clearer. In MBE wafer, material is grown by molecular beam epitaxy. Table 3.2 shows the name of the samples in the thesis.

| Sample                                                                     | Name of the sample in the thesis |

|----------------------------------------------------------------------------|----------------------------------|

| GaAs <sub>x</sub> P <sub>1-x</sub> /GaAs on On-axis Si substrate           | Wafer E                          |

| GaAs <sub>x</sub> P <sub>1-x</sub> /GaAs on Off-cut Si substrate           | Wafer F                          |

| GaAs <sub>x</sub> P <sub>1-x</sub> /thickened GaAs on Off-cut Si substrate | Wafer T                          |

| GaAs <sub>x</sub> P <sub>1-x</sub> / n+ GaAs substrate                     | Wafer n+ GaAs                    |

| GaAs <sub>x</sub> P <sub>1-x</sub> / GaP on Si substrate                   | Wafer MBE                        |

| $GaAs_xP_{1-x}$ / Polished thickened $GaAs$ on Off-cut Si substrate        | Wafer U                          |

Table 3.2: Name of the samples in this thesis.

The difference between wafer F and wafer T is the thickness of GaAs substrate. In wafer T, in thicker GaAs, which is around 6 microns, dislocations will have more space to cancel out each other. In next chapters by comparing the crystalline quality of wafer F and T, it will be shown that FWHM of wafer T is less which shows the better crystalline quality.

In wafer U the substrate has been polished. In the next chapters the crystalline quality of these wafers will be compared and reported.

Growth conditions such as temperature and precursor flow for each growth run are represented in Table 3.3.

| Run number |      |                  |      |                 |  |

|------------|------|------------------|------|-----------------|--|

|            | (°C) | AsH <sub>3</sub> | GaCl | PH <sub>3</sub> |  |

| 3957       | 660  | 15               | 15   | 85              |  |

| 3963       | 610  | 15               | 15   | 85              |  |

| 3969       | 710  | 15               | 15   | 85              |  |

| 3971       | 610  | 15               | 25   | 85              |  |

| 3979       | 610  | 25               | 25   | 75              |  |

Table 3.3: Growth conditions of sample grown for crystalline quality optimization.

Runs number 3963, 3971 and 3979 are performed at  $610\,^{\circ}$ C temperature whereas runs 3957 and 3969 are performed at higher temperature,  $660\,^{\circ}$ C and  $710\,^{\circ}$ C, respectively. The precursor flows are the same for all the runs except for 3979 in which arsine flow has been increased while phosphine flow has been decreased.

After investigating the characterization results, we can figure out the effect of growth conditions on the crystalline quality of the epitaxial layer.

### 3.2 Characterization of the grown samples

HRXRD measurement can yield information on about crystalline quality and composition and optical microscope on surface morphology of the epitaxial layer. By comparing the results of the samples and finding the best one, growth condition related to that sample could be considered as optimized growth conditions which can be used for future growth runs.

### 3.2.1 Crystal quality and composition

As it was mentioned in 2.2.1 information about crystalline quality of the epitaxial layer can be deduced from full width at half maximum (FWHM) value, in Omega scan in HRXRD. Besides, composition of the epitaxial layer can be obtained from Omega-2theta scan. Therefore, omega scan in triple axis on  $GaAs_xP_{1-x}$  layer and omega-2theta scan in double axis have been done on all the samples.

Information about HRXRD measurement is summarized in Table 3.4.

| HR         | XRD results of samples gro | wn for crystalline quality optimi                         | zation                                 |  |

|------------|----------------------------|-----------------------------------------------------------|----------------------------------------|--|

| Run number | Sample                     | GaAs <sub>x</sub> P <sub>1-x</sub> layer FWHM<br>(arcsec) | Composition $GaAs_{x}P_{1-x}$          |  |

|            | Wafer E                    | 576                                                       | GaAs <sub>0.63</sub> P <sub>0.37</sub> |  |

| 3957       | Wafer F                    | 468                                                       | GaAs <sub>0.48</sub> P <sub>0.52</sub> |  |

|            | Wafer T                    | 576                                                       | GaAs <sub>0.58</sub> P <sub>0.42</sub> |  |

|            | Wafer n+ GaAs              | 342                                                       | GaAs <sub>0.60</sub> P <sub>0.40</sub> |  |

|            | Wafer E                    | 576                                                       | GaAs <sub>0.67</sub> P <sub>0.33</sub> |  |

| 3963       | Wafer F                    | 540                                                       | GaAs <sub>0.46</sub> P <sub>0.54</sub> |  |

|            | Wafer T                    | 612                                                       | GaAs <sub>0.63</sub> P <sub>0.37</sub> |  |

|            | Wafer n+ GaAs              | 396                                                       | GaAs <sub>0.72</sub> P <sub>0.28</sub> |  |

|            | Wafer E                    | 432                                                       | GaAs <sub>0.66</sub> P <sub>0.34</sub> |  |

|            | Wafer F                    | 828                                                       | GaAs <sub>0.42</sub> P <sub>0.58</sub> |  |

| 3969       | Wafer T                    | 756                                                       | GaAs <sub>0.68</sub> P <sub>0.32</sub> |  |

| _          | Wafer MBE                  | 648                                                       | GaAs <sub>0.57</sub> P <sub>0.43</sub> |  |

| _          | Wafer n+ GaAs              | 288                                                       | GaAs <sub>0.59</sub> P <sub>0.41</sub> |  |

|            | Wafer E                    | 612                                                       | GaAs <sub>0.56</sub> P <sub>0.44</sub> |  |

|            | Wafer F                    | 504                                                       | GaAs <sub>0.59</sub> P <sub>0.41</sub> |  |

| 3971       | Wafer T                    | 936                                                       | GaAs <sub>0.56</sub> P <sub>0.44</sub> |  |

|      | Wafer MBE     | 1080 | GaAs <sub>0.40</sub> P <sub>0.60</sub> |

|------|---------------|------|----------------------------------------|

|      | Wafer n+ GaAs | 288  | GaAs <sub>0.64</sub> P <sub>0.36</sub> |

|      | Wafer E       | 540  | GaAs <sub>0.73</sub> P <sub>0.27</sub> |

|      | Wafer F       | 468  | GaAs <sub>0.90</sub> P <sub>0.10</sub> |

| 3979 | Wafer T       | 684  | GaAs <sub>0.73</sub> P <sub>0.27</sub> |

|      | Wafer U       | 468  | GaAs <sub>0.64</sub> P <sub>0.06</sub> |

|      | Wafer n+ GaAs | 396  | GaAs <sub>0.80</sub> P <sub>0.20</sub> |

Table 3.4: HRXRD results of grown samples for crystalline quality optimization.

#### 3.2.1.1 Comparing Si substrate samples in each growth run

By looking at Table 3.4 it is shown that in run 3957, comparing FWHM value for wafers E, F and T shows that wafer F has the lowest value, which is 468 arcsec and has the larger phosphorus fraction showing 52%. Wafer E shows the lowest phosphorus fraction which is 37%.

In growth 3963, again wafer F has the lowest FWHM value among the Si substrate wafers and has the largest phosphorus fraction, which is 54% among the Si substrate samples. The lowest phosphorus fraction is for wafer E, 33%.

Looking at run 3969, the lowest FWHM value belongs to wafer E and its phosphorus fraction is 34% and is the second lowest among the Si substrate wafers in this run. The lowest phosphorus fraction belongs to wafer T and is 32%.

In run 3971, the lowest FWHM value is for wafer F. The same sample shows the lowest phosphorus fraction, which is 41%.

In growth run 3979, wafer F and wafer U have the lowest FWHM value among other Si substrate wafers which is 468 arcsec whereas lowest phosphorous fraction belongs to wafer U and is 6%.

Generally, in all the growth runs n+ GaAs wafer shows lower FWHM value compared to Si substrate wafers. This is expected since the lattice mismatch between  $GaAs_xP_{1-x}$  and GaAs is lower than that between  $GaAs_xP_{1-x}$  and Si.

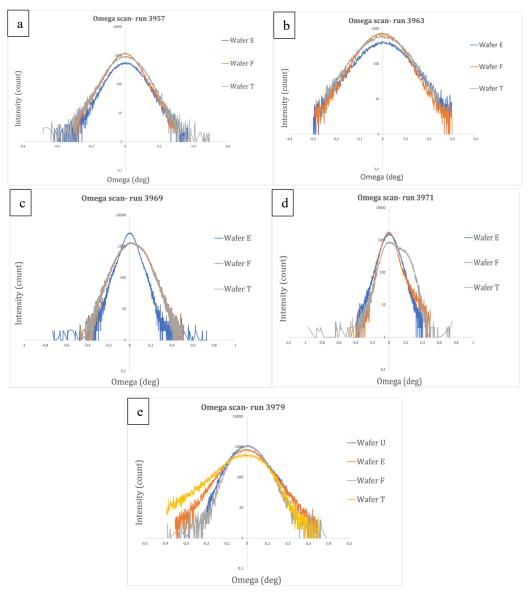

Figure 3-1 shows the Omega scan on  $GaAs_xP_{1-x}$  layer in triple axis of samples from different growth runs and results are plotted in logarithmic scale.

Figure 3-1: Omega scan of samples in different runs.

The most important information can be deduced from Omega scan is FWHM value which shows the crystalline quality of the wafer to some extent, and related data is reported in Table 3.4.

In Figure 3-1 (a) run 3957, wafer E and T have higher FWHM values which indicates the poorer crystalline quality. The same result is true for run 3963 and Figure 3-1 (b) shows wafer E and T have higher FWHM value. Looking at figure 3-1 (c) it shows in run 3969 wafer E has the lowest FWHM value which indicates the best crystalline quality among others and wafer F in run 3971 has the lowest FWHM value as it can be seen in Figure 3-1 (d). In run 3979 wafer F and U have the lowest FWHM value indicating better crystalline quality among other wafers in this run as it can be seen in Figure 3-1 (e).

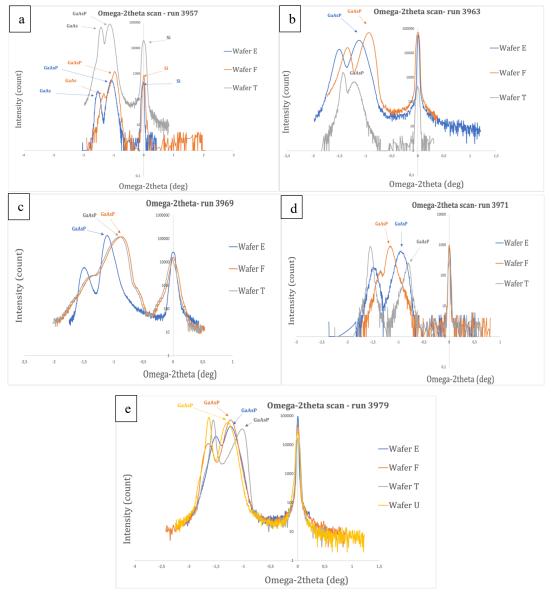

Omega- 2theta scan in double axis of Si substrate samples for each run has been done and results are plotted in logarithmic scale shown in Figure 3-2.

Figure 3-2: Omega-2theta scan of samples in different runs.

As Figure 3-2 (a) shows in run 3957, wafer T has the highest intensity and even though wafer F has the lowest FWHM value, it does not have the highest intensity.

In Figure 3-2 (b), highest intensity in run 3963 belongs to wafer F and it also has the lowest FWHM values. In addition, P-fraction of wafer F is quite high.

In run 3969, wafer E has the highest intensity among others and lowest FWHM value was also for the same wafer in this run indicating the best crystalline quality.

Figure 3-2 (d) shows in run 3971 wafer F has the highest intensity and it has the lowest FWHM value. In addition, p-fraction of wafer F is the lowest among other wafers in this run.

Looking at Figure 3-2 (e) in run 3979 wafer F has the highest intensity and wafer U has the second highest intensity. These two wafers have the same FWHM value, which is 468 arcsec, but p-fraction of wafer F which is 10% is higher that of wafer U, which is 6%.

Looking at HRXRD characterization of different wafers in each growth run, wafer F in all the growth runs and wafer U from run 3979 shows better crystalline quality among the Si substrate wafers.

# 3.2.1.2 Comparin different growth runs

FWHM values of wafers from different growth runs are reported in Table 3.5 to make it easier for comparison and results of Omega scan are plotted in logarithmic scale shown in Figure 3-3.

| FWHM value Comparison (arcsec) |         |         |         |               |           |  |  |  |

|--------------------------------|---------|---------|---------|---------------|-----------|--|--|--|

| Run number                     | Wafer E | Wafer F | Wafer T | Wafer n+ GaAs | Wafer MBE |  |  |  |

| 3957                           | 576     | 468     | 576     | 342           | -         |  |  |  |

| 3963                           | 576     | 540     | 612     | 396           | -         |  |  |  |

| 3969                           | 432     | 828     | 756     | 288           | 648       |  |  |  |

| 3971                           | 612     | 504     | 936     | 288           | 1081      |  |  |  |

| 3979                           | 540     | 468     | 684     | 396           | -         |  |  |  |

Table 3.5: FWHM values for different wafers of different runs.

Figure 3-3: Omega scan plots of a) wafer E, b) wafer F, c) Wafer T, d) n+ GaAs wafer and e) wafer MBE of different growth runs.

Figure 3-3 (a) shows among all wafer E from different runs, wafer E in run 3969 has the lowest FWHM value indicating the best crystalline quality.

Comparing wafer F from different growth runs shows wafer F from run 3979 has the lowest FWHM value and wafer F from run 3969 has the highest FWHM value indicating the worse crystalline quality as Figure 3-3 (b) shows.

Figure 3-3 (c) shows wafer T from run 3957 has the lowest FWHM value and run 3971 has the highest FWHM value among other growth runs.

Results of Omega-2theta scans in double axis for different runs are plotted in logarithmic scale in Figure 3-4. Crystalline quality and composition of the epi-layer are information which can be deduced from Omega-2theta scan.

Figure 3-4: Omega-2theta plots of a) wafer E, b) wafer F, c) wafer T d) wafer n+ GaAs and e) wafer MBE of different runs.

Figure 3-4 (a) shows wafer E from run 3969 has the highest intensity among other runs which indicates a good crystalline quality, and the same wafer had the lowest FWHM value which shows the same results.

As it is shown in Figure 3-4 (b), wafer F from run 3969 has the highest intensity and the second highest intensity belongs to run 3979.

Wafer F from run 3969 has a high FWHM value, which is 828 arcsec and looking at Table 3.5 its p-fraction is 58%. Wafer F from run 3979 has the lowest FWHM value which indicates the best crystalline quality. Looking at Table 3.4, the P-fraction of this sample is 10%, so one can conclude by decreasing the flow of  $PH_3$ , from 85 sccm in run 3969 to 75 sccm in run 3979 the crystalline quality is improved.

Figure 3-4 (c) shows wafer T from run 3969 has the highest intensity while it has a high FWHM value and 32% P-fraction. The second highest intensity belongs to wafer T from run 3957, with the lowest FWHM value among other runs. Temperature in runs 3969 and 3957 is 710 °C and 660 °C, respectively, so it seems decreasing the temperature will increase the crystalline quality of the epi-layer. For n+ GaAs substrate samples, the highest intensity is for run 3969 and FWHM value of this sample is the lowest, so among n+ GaAs substrate samples run 3969 gives the best crystalline quality. Figure 3-4 (e) shows run 3963 has the higher intensity and has lower FWHM value compared to run 3971 which indicates the better crystalline quality.

#### 3.2.2 Surface morphology

Surface morphology of the sample reflects the crystalline quality to some extent. Basically, large number of pits and hillocks could affect the performance of the device in a negative way. So, a smoother surface with less roughness is desired for device fabrication.

The morphology of all samples is studied with an optical microscope and the results are shown below.

### 3.2.2.1 Comparing Si substrate samples in each growth run

First, Si substrate samples from each run are investigated and compared with each other to figure out the best substrate.

Figure 3-5: Top view of Si substrate wafers in run 3957.